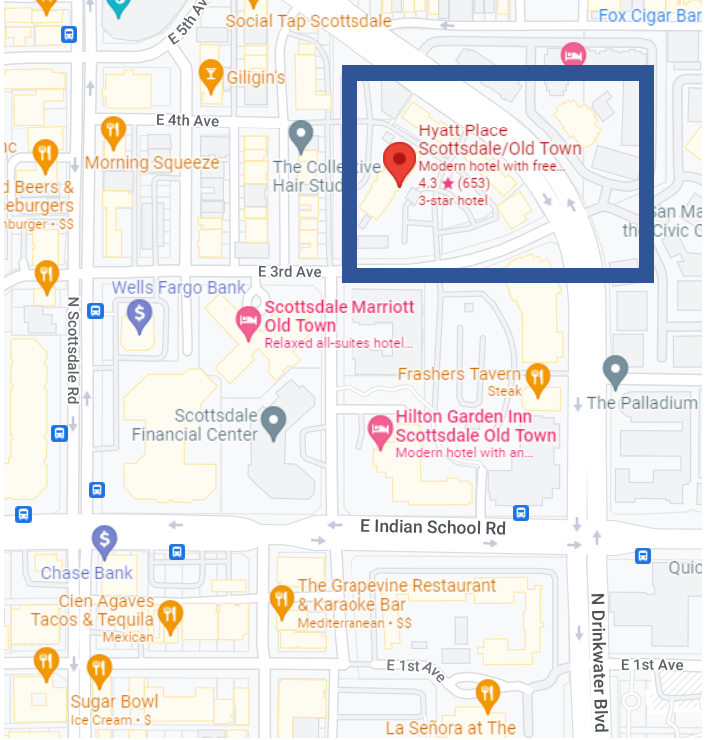

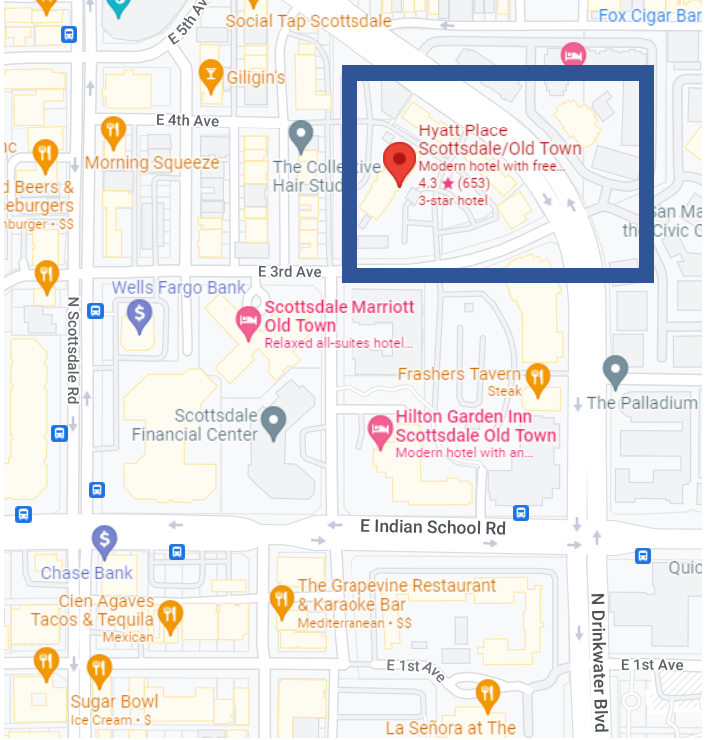

Location

-

- Location: Hyatt Place Scottsdale/Old Town, 7300 East Third Avenue, Scottsdale, AZ 85251

International Workshop on Secure RISC-V

(SECRISC-V) Architecture Design Exploration

seeks original research papers on the design,

implementation, verification, and evaluation of

micro-architecture security features, hardware-assisted

security techniques, and secure executions around the RISC-V

instruction set architecture (ISA).

Brief Bio: Nikil D. Dutt is a Chancellor’s Professor at the University of California, Irvine, with academic appointments in the CS, EECS, and Cognitive Sciences departments. He received a B.E.(Hons) in Mechanical Engineering from the Birla Institute of Technology and Science, Pilani, India in 1980, an M.S. in Computer Science from the Pennsylvania State University in 1983, and a Ph.D. in Computer Science from the University of Illinois at Urbana-Champaign in 1989. He is affiliated with the following Centers at UCI: Center for Embedded Computer Systems (CECS), Center for Cognitive Neuroscience and Engineering (CENCE), California Institute for Telecommunications and Information Technology (Calit2), the Center for Pervasive Communications and Computing (CPCC), and the Laboratory for Ubiquitous Computing and Interaction (LUCI).

Brief Bio: Nikil D. Dutt is a Chancellor’s Professor at the University of California, Irvine, with academic appointments in the CS, EECS, and Cognitive Sciences departments. He received a B.E.(Hons) in Mechanical Engineering from the Birla Institute of Technology and Science, Pilani, India in 1980, an M.S. in Computer Science from the Pennsylvania State University in 1983, and a Ph.D. in Computer Science from the University of Illinois at Urbana-Champaign in 1989. He is affiliated with the following Centers at UCI: Center for Embedded Computer Systems (CECS), Center for Cognitive Neuroscience and Engineering (CENCE), California Institute for Telecommunications and Information Technology (Calit2), the Center for Pervasive Communications and Computing (CPCC), and the Laboratory for Ubiquitous Computing and Interaction (LUCI).

Brief Bio: Rosario Cammarota ("Ro") is a Principal Engineer at Intel Labs, where he leads the effort on privacy-enhancing cryptographic technologies, their application, and standardization. Ro's research is at the intersection between cryptography and computing, focusing on fully homomorphic encryption, secure multi-party computation, and their application to artificial intelligence and statistics. He received his Ph.D. degree in Computer Science from the University of California, Irvine. Ro is a Senior Member of IEEE. He is a prolific author and inventor. His research appears in journals and conferences such as ACM TECS, DAC, IEEE HOST, among others. He is one of the recipients of the SRC Outstanding Industry Liaison Awards in 2017, 2018, and 2019.

Brief Bio: Rosario Cammarota ("Ro") is a Principal Engineer at Intel Labs, where he leads the effort on privacy-enhancing cryptographic technologies, their application, and standardization. Ro's research is at the intersection between cryptography and computing, focusing on fully homomorphic encryption, secure multi-party computation, and their application to artificial intelligence and statistics. He received his Ph.D. degree in Computer Science from the University of California, Irvine. Ro is a Senior Member of IEEE. He is a prolific author and inventor. His research appears in journals and conferences such as ACM TECS, DAC, IEEE HOST, among others. He is one of the recipients of the SRC Outstanding Industry Liaison Awards in 2017, 2018, and 2019.

Brief Bio: Andreas Gerstlauer is a Professor, holder of the Engineering Foundation Endowed Faculty Fellowship in Engineering, and the Associate Chair for Academic Affairs in the Department of Electrical & Computer Engineering at The University of Texas at Austin. He received a M.S. degree in Electrical Engineering from the University of Stuttgart, Germany in 1997 and his M.S. and Ph.D. degrees in Information and Computer Science from the University of California, Irvine in 1998 and 2004, respectively. He is co-author on 3 books and more than 100 conference and journal publications, and he has presented in numerous conference and industrial tutorials. His work was recognized by a 2016-2017 Humboldt Research Fellowship, the Best Research Paper Award at the 2016 Design Automation Conference (DAC), the Best Paper Award at the 2015 International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS), several best paper nominations from, among others, DAC, DATE and HOST, and as one of the most influential contributions in 10 years at DATE in 2008.

Brief Bio: Andreas Gerstlauer is a Professor, holder of the Engineering Foundation Endowed Faculty Fellowship in Engineering, and the Associate Chair for Academic Affairs in the Department of Electrical & Computer Engineering at The University of Texas at Austin. He received a M.S. degree in Electrical Engineering from the University of Stuttgart, Germany in 1997 and his M.S. and Ph.D. degrees in Information and Computer Science from the University of California, Irvine in 1998 and 2004, respectively. He is co-author on 3 books and more than 100 conference and journal publications, and he has presented in numerous conference and industrial tutorials. His work was recognized by a 2016-2017 Humboldt Research Fellowship, the Best Research Paper Award at the 2016 Design Automation Conference (DAC), the Best Paper Award at the 2015 International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS), several best paper nominations from, among others, DAC, DATE and HOST, and as one of the most influential contributions in 10 years at DATE in 2008.

Brief Bio:Antonino Tumeo is a Chief Scientist at Pacific Northwest National Laboratory. He received the M.S degree in Informatic Engineering, in 2005, and the Ph.D degree in Computer Engineering, in 2009, from Politecnico di Milano in Italy. Since February 2011, he has been a research scientist in the PNNL's High Performance Computing group. He Joined PNNL in 2009 as a post doctoral research associate. Previously, he was a post doctoral researcher at Politecnico di Milano. His research interests are modeling and simulation of high performance architectures, hardware-software codesign, FPGA prototyping and GPGPU computing.

Brief Bio:Antonino Tumeo is a Chief Scientist at Pacific Northwest National Laboratory. He received the M.S degree in Informatic Engineering, in 2005, and the Ph.D degree in Computer Engineering, in 2009, from Politecnico di Milano in Italy. Since February 2011, he has been a research scientist in the PNNL's High Performance Computing group. He Joined PNNL in 2009 as a post doctoral research associate. Previously, he was a post doctoral researcher at Politecnico di Milano. His research interests are modeling and simulation of high performance architectures, hardware-software codesign, FPGA prototyping and GPGPU computing.

Submission of early work is encouraged. The RISC-V ISA based topics of specific interest for the workshop include, but are not limited to:

We are adding a poster session to this year's workshop for greater active student participation.